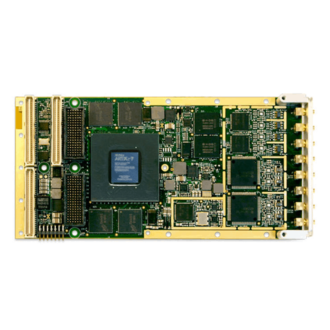

Le XA-AWG est un module XMC comportant huit Canaux DAC 16 bits, 250 MSPS conçus pour les stations de base des réseaux cellulaires, la transmission en diversité et les communications large bande.

Les méthodes de déclenchement flexibles incluent le comptage de trames, le déclenchement logiciel ou le déclenchement externe. L’horloge d’échantillonnage est soit une horloge externe soit une horloge PLL programmable intégrée.

Le contrôle d’acquisition des données, le traitement du signal, la mise en mémoire tampon et les fonctions d’interface système sont implémentées dans un FPGA Xilinx Artix-7. Deux mémoires de 256Mx16 fournissent une mémoire tampon de données et une mémoire de calcul FPGA.

Le micrologiciel du FPGA Artix-7 peut être entièrement personnalisé à l’aide de VHDL et / ou Xilinx System Generator avec le jeu d’outils FrameWork Logic.

L’interface PCI Express 2.0 prend en charge des débits de données jusqu’à 1600 Mo/s pour des données continues sans tampon ou des données en rafale. Lors de l’utilisation d’une configuration standard impliquant des données en mémoire tampon DDR3, un débit de données continu jusqu’à 1600 Mo/s est supporté.