Le module FMC-SDF comprend quatre ADCs et DACs à échantillonnage simultané avec un noyau informatique FPGA. Les ADC haute résolution sigma-delta et les DAC haute résolution supportent des applications d’acquisition dynamique haut de gamme telles que l’acquisition de données audio, ATE et sismique.

Les commandes d’horloge et de déclenchement incluent le support de boucle d’asservissement cohérente, de blocs comptés, de déclenchement logiciel et de déclenchement externe. L’horloge de fréquence d’échantillonnage est soit une horloge externe, soit une source d’horloge PLL programmable embarquée

La consommation FMC-SDF est de 15 W pour un fonctionnement typique. Le module peut être refroidi par conduction en utilisant la norme VITA20 et une plaque d’étalement thermique. Les niveaux de rugosité pour un fonctionnement à grande température sont disponibles de -40 à + 85 ° C et de 0,1 g2 / Hz. Un revêtement vernis épargne est également disponible.

La logique de support en VHDL est fournie pour l’intégration avec les cartes porteuses FPGA. Un support spécifique pour les cartes de support innovantes comprend l’intégration avec les outils Framework Logic qui prennent en charge les développeurs VHDL et Matlab. Le Matlab BSP prend en charge le développement en temps réel du matériel dans la boucle à l’aide du diagramme synoptique Simulink environnement avec Xilinx System Generator pour le FMC intégré avec la carte FPGA.

Les outils logiciels pour les cartes porteuses Innovative incluent des bibliothèques de développement C ++, d’hôte et des pilotes pour Windows et Linux, 32/64 bits incluant des variantes RTOS. Des exemples d’application illustrant les caractéristiques du module sont fournis.

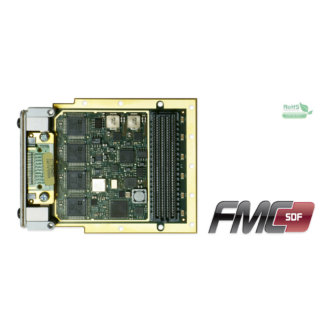

FMC-SDF - Module FMC, 4 voies ADC 625 Ke/s 24 bits et 2 voies DAC18 bits

Fonctionnalités principales

- Quatre canaux d’entrée A/D

- Plage d’entrée ± 5V

- A/D 625 kSPS, 24 bits

- Entrées différentielles

- Deux canaux de sortie D / A

- Temps de stabilisation 2.1μs, D/A 18 bits

- Plage de sortie ± 5V

- Entrée du tachymètre

- Trigger Schmitt pour tolérance de glitch

- Peut être configuré pour fonctionnement différenciel

- Horloges d’échantillonnage et timing et contrôles

- Référence 10 MHz, ± 250 ppb de stabilité intégrée

- PLL programmable

- Fréquence d’horloge programmable aussi faible que 3,05 kHz

- Intégré aux Triggers FMC

- Module FMC, VITA 57.1

- Nombre de broches élevé Aucun SERDES requis

- Compatible avec le VADJ 2.5V

- Moniteur de puissance et contrôle

- 15 W typique

- Refroidissement par conduction suivant VITA 20

- Évaluations environnementales pour -40 à 85C

- Vibration aléatoire 9g RMS sinus, 0,1g2/Hz