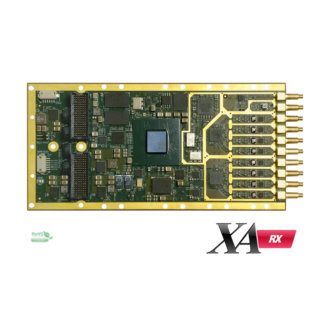

The XA-RX is an XMC IO module featuring eight 16-bit, 125 MSPS A/D channels designed for high speed stimulus-response, ultrasound, and RADAR.

Flexible trigger methods include counted frames, software triggering and external triggering. The sample rate clock is either an external clock or on- board programmable PLL clock source.

Data acquisition control, signal processing, buffering, and system interface functions are implemented in a Xilinx Artix-7 FPGA device. Two 256Mx16 memories provide data buffering and FPGA computing memory.

The logic can be fully customized using VHDL and MATLAB using the FrameWork Logic toolset. The MATLAB BSP supports real-time hardware-in-the- loop development using the graphical, block diagram Simulink environment with Xilinx System Generator.

The PCI Express 2.0 interface supports continuous data rates up to 3200 MB/ s between the module and the host. A flexible data packet system implemented over the PCIe interface provides both high data rates to the host that is readily expandable for custom applications.