The XA-500M is an XMC IO module featuring two 14-bit, 500 MSPS A/D channels and two 16-bit, 615 MSPS DAC channels designed for high speed stimulus-response, ultrasound, and servo control applications.

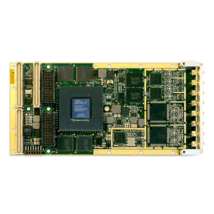

Flexible trigger methods include counted frames, software triggering and external triggering. The sample rate clock is either an external clock or on-board programmable PLL clock source.

Data acquisition control, signal processing, buffering, and system interface functions are implemented in a Xilinx Artix-7 FPGA device. Two 256Mx16 memories provide data buffering and FPGA computing memory.

The Artix-7 FPGA device firmware can be fully customized using VHDL and/or Xilinx System Generator along with the FrameWork Logic toolset.

The PCI Express 2.0 interface supports data rates up to 1600 MB/s for unbuffered continuous data or burst data streams. When using a standard configuration involving DDR3 buffered data, a continuous data rate up to 1600 MB/s is supported.